Tensor Core 是什么:2026 混合精度计算原理与 AI 应用全面解析

一句话定义

Tensor Core 是 NVIDIA GPU 中专为矩阵乘法加速的硬件单元,通过混合精度计算在单次时钟周期内完成大规模并行运算,极大提升 AI 训练与推理效率。

技术原理:从标量到矩阵的算力跃迁

要真正理解"Tensor Core 是什么”,我们必须深入其微观架构,剖析它如何颠覆了传统图形处理器(GPU)的计算逻辑。在 Tensor Core 诞生之前,GPU 的核心计算单元是 CUDA Core,它们擅长处理标量(Scalar)或向量(Vector)运算,即一次操作处理一个或一组数据。然而,深度学习的本质是海量的矩阵乘法(Matrix Multiplication),传统方式如同让无数个小工一个个搬运砖块,虽然人多势众,但效率遭遇瓶颈。Tensor Core 的出现,相当于直接调用了一台巨型起重机,一次性搬运整面墙的砖块。

核心工作机制:D = A × B + C

Tensor Core 的核心工作原理可以浓缩为一个特定的数学公式:D = A × B + C。

在这个公式中:

- A 和 B 是两个输入矩阵(Matrix)。

- C 是一个累加矩阵(Accumulator Matrix)。

- D 是最终输出的结果矩阵。

在传统的 CUDA Core 架构下,完成这样一个矩阵乘加运算需要分解为成百上千个独立的浮点运算指令,每个指令都需要经过取指、解码、执行、写回等多个流水线阶段。而 Tensor Core 将这一整个复杂的数学过程固化在硬件电路中。在一个时钟周期(Clock Cycle)内,一个 Tensor Core 就能直接完成整个 4×4 矩阵的乘法并加上累加值。

以 NVIDIA Volta 架构(首个引入 Tensor Core 的架构)为例,每个流式多处理器(SM)包含 8 个 Tensor Core。在一个时钟周期内,单个 SM 就能执行 64 次浮点乘加运算(FMA)。如果我们将视野扩大到整个 GPU,这种并行能力的提升是指数级的。到了后续的 Ampere 和 Hopper 架构,矩阵的尺寸支持变得更加灵活(如 16×16, 32×32 甚至更大),且支持的精度格式也更加丰富。

混合精度计算:速度与精度的完美平衡

Tensor Core 最革命性的特性在于其对混合精度(Mixed Precision)的原生支持。这是理解其高性能的关键。在传统的高性能计算(HPC)中,为了追求极致的准确性,通常使用双精度浮点数(FP64)或单精度浮点数(FP32)。然而,在深度学习领域,神经网络的训练和推理对数值精度的敏感度远低于科学计算。过高的精度不仅浪费显存带宽,更会导致计算吞吐量大幅下降。

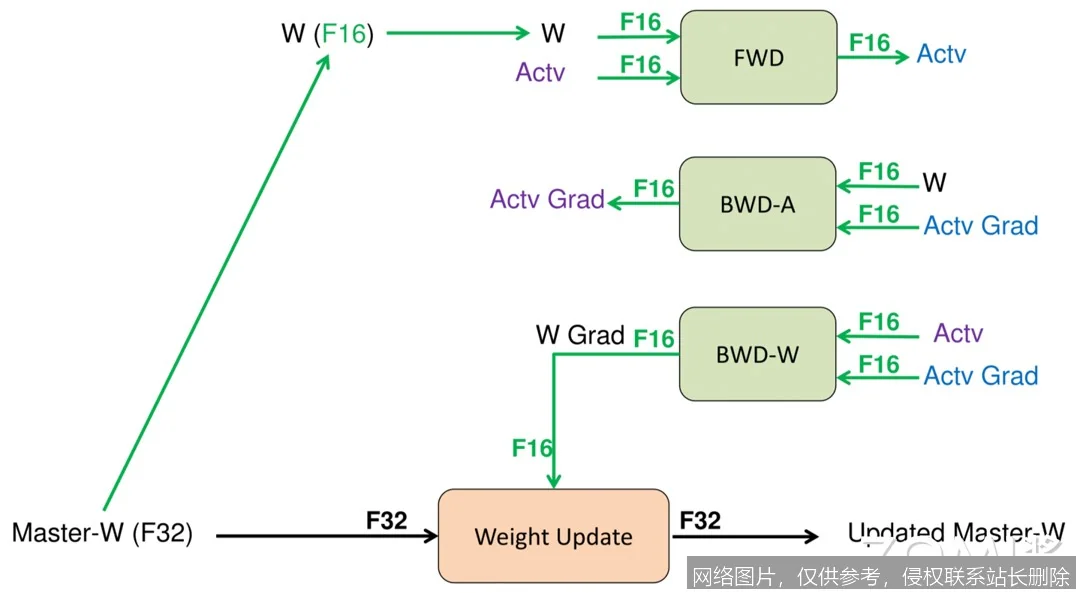

Tensor Core 采用了一种巧妙的策略:

- 输入阶段(低精度):矩阵 A 和 B 使用低精度格式,通常是半精度(FP16)或脑浮点格式(BF16)。这使得数据量减半,传输速度加倍,计算电路更加简化。

- 累加阶段(高精度):中间结果的累加以及最终输出 D,使用高精度的 FP32 格式。这一步至关重要,因为它防止了在成千上万次运算中误差的累积,确保了模型收敛的稳定性和最终结果的准确性。

这种“低精度计算、高精度累加”的模式,就像是在建造大楼时,用快速测量的卷尺(低精度)来切割大部分木材以提高效率,但在关键的承重节点校准上,依然使用激光测距仪(高精度)来确保整体结构不倒塌。通过这种方式,Tensor Core 相比纯 FP32 的 CUDA Core,理论算力提升了数十倍甚至上百倍。

与传统方法的对比:流水线与专用引擎

为了更直观地理解差异,我们可以做一个类比。

假设我们要计算 $1000 \times 1000$ 的矩阵乘法:

- CUDA Core(传统方法): 就像是一个拥有数千名普通算术家的广场。每个人只能做 $a \times b + c$ 这样简单的运算。指挥官(调度器)必须不断地分发任务,协调数万人同时工作,不仅要处理计算,还要花费大量时间在沟通和数据搬运上。虽然人多,但组织成本极高。

- Tensor Core(现代方法): 就像是引入了几十个超级计算引擎。每个引擎内部已经预设好了复杂的齿轮组,只要把两堆数字(矩阵块)倒进去,瞬间就会吐出一个结果块。它省去了大量的指令调度开销,将晶体管主要用于纯粹的数据通路和计算逻辑,而非控制逻辑。

从硬件资源分配来看,CUDA Core 保留了完整的控制单元、缓存层级和复杂的分支预测机制,以适应通用的图形渲染和逻辑判断;而 Tensor Core 则是高度专用的“计算器”,去除了不必要的通用性负担,专为密集矩阵运算优化。这种专用化(Specialization)正是摩尔定律放缓背景下,提升算力的核心路径。

核心概念:构建混合精度的知识图谱

深入理解 Tensor Core,需要掌握一系列与之紧密相关的专业术语。这些概念共同构成了现代 AI 计算的基石。

关键术语解析

1. 混合精度(Mixed Precision)

指在同一个计算过程中同时使用不同精度的数据类型。在 AI 语境下,特指利用 FP16/BF16 进行矩阵乘法,利用 FP32 进行权重更新和累加。这不仅加快了计算速度,还减少了显存占用,使得在有限显存下训练更大的模型成为可能。

2. FP16 (Half Precision) 与 BF16 (Bfloat16)

- FP16:IEEE 754 标准的半精度浮点数,占用 16 位。其中 1 位符号位,5 位指数位,10 位尾数位。它的动态范围较小,容易在梯度极小或极大时发生溢出(Overflow)或下溢(Underflow)。

- BF16:Google 提出的脑浮点格式,同样占用 16 位,但结构与 FP32 更接近(1 位符号位,8 位指数位,7 位尾数位)。BF16 牺牲了部分精度,但保留了与 FP32 相同的动态范围,因此在深度学习训练中比 FP16 更稳定,无需复杂的损失缩放(Loss Scaling)技巧即可直接替换 FP32。

3. Tensor Float 32 (TF32)

这是 NVIDIA Ampere 架构引入的一种独特格式。它在输入时类似 FP16 的紧凑性,但在内部计算时自动扩展精度,行为上接近 FP32。TF32 允许用户在不修改代码的情况下,自动获得接近 FP16 的速度和接近 FP32 的精度,极大地降低了混合精度编程的门槛。

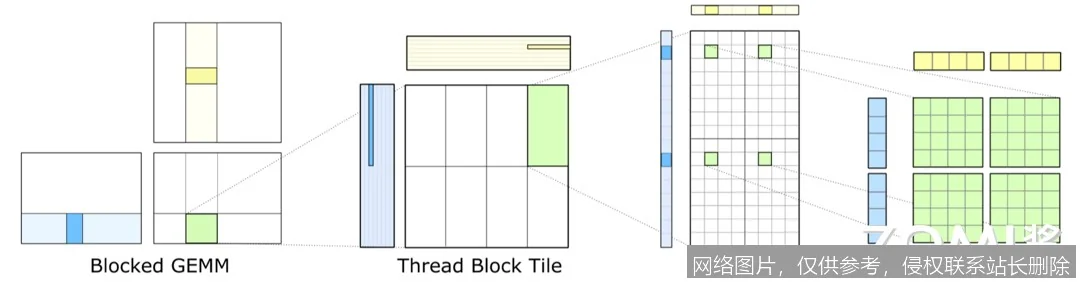

4. GEMM (General Matrix Multiply)

通用矩阵乘法,是线性代数中最基础的操作,也是卷积神经网络(CNN)和 Transformer 模型中最耗时的部分。Tensor Core 本质上就是一个超高速的 GEMM 引擎。

概念关系图谱

可以将这些概念想象成一个金字塔结构:

- 塔尖(应用层):大语言模型(LLM)、计算机视觉、推荐系统。它们依赖高效的算力。

- 塔身(算法层):混合精度训练策略、自动微分、梯度裁剪。这些算法利用了硬件特性。

- 塔基(硬件层):Tensor Core。它是物理实体,直接执行矩阵运算。

- 土壤(数据表示):FP16, BF16, TF32, INT8, FP8。不同的数据格式决定了进入塔基的“原料”形态。

Tensor Core 位于中心,向上支撑算法,向下兼容多种数据格式。没有合适的数值格式(如 BF16),Tensor Core 的威力无法完全释放;而没有 Tensor Core,混合精度算法只能退化为软件模拟,失去性能优势。

常见误解澄清

误解一:"Tensor Core 会牺牲模型精度,导致训练失败。”

澄清: 这是一个早期的担忧。实际上,由于引入了 FP32 的主控精度(Master Weights)和高精度累加器,现代混合精度训练的收敛效果往往与纯 FP32 相当,甚至在某些情况下,低精度带来的微小噪声有助于模型跳出局部最优解,提升泛化能力。只要使用成熟的框架(如 PyTorch AMP),精度损失几乎可以忽略不计。

误解二:“只有训练才需要 Tensor Core,推理不需要。”

澄清: 恰恰相反。推理阶段对延迟(Latency)和吞吐量(Throughput)极其敏感。Tensor Core 支持 INT8 和 FP8 量化推理,能在几乎不损失精度的前提下,将推理速度提升数倍,显著降低云端部署成本。对于实时语音识别、自动驾驶等场景,Tensor Core 是不可或缺的。

误解三:"Tensor Core 是 NVIDIA 独有的魔法,其他厂商没有类似技术。”

澄清: 虽然"Tensor Core"是 NVIDIA 的商标,但“矩阵加速单元”的概念已成为行业共识。AMD 的 Matrix Cores (in CDNA/RDNA architectures)、Google TPU 的 Matrix Multiply Unit (MXU)、以及华为昇腾的 Cube Unit,其核心设计思想均与 Tensor Core 异曲同工,都是为了加速矩阵运算。只是各家在指令集、支持的精度和优化策略上有所不同。

实际应用:从实验室到产业界的落地

Tensor Core 不仅仅是一个硬件参数,它已经深刻改变了 AI 产品的研发流程和部署模式。以下是其在实际场景中的典型应用。

典型应用场景

1. 大语言模型(LLM)的训练与微调

随着模型参数量从亿级迈向万亿级(如 Llama 3, GPT-4 系列),显存容量和计算带宽成为最大瓶颈。利用 Tensor Core 的 BF16 支持,研究人员可以在相同的显卡数量下,训练规模大一倍的模型,或者将训练时间从数月缩短至数周。例如,在微调(Fine-tuning)过程中,结合 LoRA(Low-Rank Adaptation)技术与 Tensor Core 的加速,使得在消费级显卡上运行原本需要集群才能完成的微调任务成为可能。

2. 高分辨率图像生成与扩散模型

Stable Diffusion、Midjourney 等扩散模型涉及大量的去噪迭代步骤,每一步都包含繁重的卷积和注意力机制运算。Tensor Core 能够加速这些矩阵操作,将生成一张高清图片的时间从几十秒压缩到几秒甚至毫秒级,实现了实时的 AI 绘画体验。

3. 自动驾驶感知系统

自动驾驶汽车需要在毫秒级时间内处理来自摄像头、激光雷达的多路传感器数据,进行目标检测和路径规划。NVIDIA DRIVE 平台广泛利用 Tensor Core 进行低精度(INT8/FP8)推理,在保证安全精度的前提下,大幅降低功耗,满足车规级芯片的严苛要求。

4. 科学计算与药物发现

除了 AI,Tensor Core 也被应用于分子动力学模拟、气候预测等领域。通过将这些科学问题转化为矩阵运算形式(如求解偏微分方程),科学家可以利用 Tensor Core 的巨大算力加速新药筛选过程,将原本需要几年的模拟缩短至几天。

代表性产品与项目案例

- NVIDIA H100 / H200 GPU: 基于 Hopper 架构,配备了第四代 Tensor Core,专门针对 Transformer 引擎进行了优化,支持 FP8 精度,是目前全球大模型训练的主力军。

- NVIDIA RTX 4090: 面向消费者的旗舰显卡,拥有大量的第四代 Tensor Core,使得个人开发者和本地游戏玩家也能体验到顶级的 AI 生成能力和 DLSS(深度学习超级采样)技术。

- Megatron-LM & DeepSpeed: 微软与 NVIDIA 合作开发的深度学习库,深度集成了 Tensor Core 的特性,通过张量并行(Tensor Parallelism)和数据并行技术,实现了千卡集群的高效协同训练。

使用门槛和条件

尽管 Tensor Core 功能强大,但要充分发挥其效能,并非简单的“开箱即用”,需要满足一定的软硬件条件:

- 硬件要求: 必须使用 Volta 架构(V100)及之后的 NVIDIA GPU(如 T4, A100, H100, RTX 20/30/40 系列)。旧款 GPU(如 Pascal 架构的 P100)不支持硬件级 Tensor Core。

- 软件栈支持: 需要安装适配的 CUDA Toolkit(通常版本需在 10.0 以上)和 cuDNN 库。应用程序必须调用相应的 API(如 cublasGemmEx)或通过高层框架(PyTorch, TensorFlow)启用自动混合精度(AMP)。

- 代码适配: 虽然现代框架已能自动识别并利用 Tensor Core,但在自定义算子开发或极端性能优化场景下,开发者仍需了解内存对齐(Memory Alignment)、数据布局(NHWC vs NCHW)等细节,以避免因数据格式不匹配导致 Tensor Core 无法激活,回退到低效的 CUDA Core 模式。

- 模型兼容性: 极少数对数值极度敏感的老旧模型可能不适合混合精度,需要进行针对性的测试和调整。

延伸阅读:通往算力巅峰的进阶之路

对于希望进一步探索"Tensor Core 是什么”及其背后广阔天地的学习者,以下路径和资源将助您从入门走向精通。

相关概念推荐

在掌握 Tensor Core 的基础上,您可以进一步研究以下关联领域,它们共同构成了现代高性能计算(HPC)的版图:

- CUDA Programming Model: 理解线程束(Warp)、共享内存(Shared Memory)和内存合并访问,是优化 Tensor Core 输入数据的前提。

- Quantization Aware Training (QAT): 量化感知训练,研究如何在训练阶段就模拟低精度环境,以便更好地发挥 Tensor Core 在 INT8/FP8 下的推理性能。

- Sparse Computing(稀疏计算): 第二代及以后的 Tensor Core 支持结构化稀疏(Structured Sparsity),即跳过零值计算,理论上可再提升两倍性能。了解稀疏算法与硬件的配合至关重要。

- Interconnect Technologies (NVLink, InfiniBand): 当单卡算力不足时,如何通过高速互联技术将多个 Tensor Core 集群化,是解决超大规模模型训练的关键。

进阶学习路径

- 基础阶段: 阅读 NVIDIA 官方博客关于 Volta/Ampere/Hopper 架构的介绍文章,理解基本架构图。

- 实践阶段: 使用 PyTorch 的

torch.cuda.amp模块,对一个标准的 CNN 或 Transformer 模型进行混合精度训练实验,对比开启前后的显存占用和训练速度。 - 深入阶段: 研读 NVIDIA CUTLASS 库的文档和源码。CUTLASS 是 NVIDIA 开源的用于实现高效矩阵乘法的 C++ 模板库,它展示了如何在代码层面精细控制 Tensor Core 的行为。

- 专家阶段: 关注 GTC (GPU Technology Conference) 的技术演讲视频,特别是关于 Compiler Optimization(编译器优化)和 Kernel Fusion(算子融合)的主题,了解如何让编译器自动生成最高效的 Tensor Core 指令。

推荐资源和文献

- 官方文档: NVIDIA CUDA C++ Programming Guide 和 NVIDIA Deep Learning Performance Guide。这是最权威的一手资料,详细列出了各代 Tensor Core 的规格和支持的指令。

- 经典论文:

- "Mixed Precision Training" (Micikevicius et al., 2017) - 奠定了混合精度训练理论基础的经典之作。

- "An In-Depth Look at Mixed Precision Training" (NVIDIA Whitepaper) - 官方发布的深度白皮书,解释了工程实现细节。

- 开源项目: GitHub 上的

NVIDIA/cutlass和pytorch/examples中的 AMP 示例代码。通过阅读高质量源码,能最快地理解理论如何转化为生产力。 - 社区论坛: NVIDIA Developer Forums 和 Stack Overflow 的 CUDA 标签。这里汇聚了全球开发者在实际应用中遇到的坑和解决方案,是解决实际问题的宝库。

综上所述,Tensor Core 不仅是 NVIDIA 硬件演进史上的里程碑,更是推动整个人工智能产业从“可用”走向“普及”的关键引擎。它通过巧妙的混合精度设计和专用的矩阵架构,打破了算力的物理壁垒。对于每一位 AI 从业者而言,深入理解 Tensor Core,就是掌握了开启下一代智能应用大门的钥匙。在未来的 2026 年乃至更远的时间里,随着精度的进一步降低(如 FP4)和稀疏化的深入,Tensor Core 及其继任者们将继续重塑我们构建智能世界的方式。

相关推荐

- 【AI词典】卷积神经网络CNN - 一种用于图像处理的深度学习模型

- 【AI词典】深度学习 - 基于神经网络的机器学习方法

- 【AI词典】神经网络 - 受生物启发的计算模型

- 对齐税:AI时代,你的每一次选择都在支付“校准成本”

- 【AI词典】知识图谱 - 结构化语义知识库

- Tensor Core 是什么:2026 混合精度计算原理与 AI 应用全面解析

- 【AI词典】向量数据库 - 专为向量化数据设计的高效存储检索系统

- 【AI词典】PEFT参数高效微调 - 高效调整大模型参数的微调技术

- 【AI词典】DPO直接偏好优化 - 无需强化学习的对齐优化方法

- 【AI词典】LoRA低秩适应 - 大语言模型高效微调方法